Ultra ATA Timing

Integrated Drive Electronics (Advanced Technology Attachment)

[IDE Bus Description]

[IDE Interface

ICs]

[IDE

Connectors] [Hard Drive Manufacturers]

[ATA Bus

Standards]

[Personal Computer Buses]

[Home]

|

Nominally called the IDE (Integrated Drive Electronics) bus; how

ever it's more correctly known as the ATA (Advanced Technology

Attachment) specification [ATA Bus]. The IDE bus is used in Personal

Computers [PCs] as a hard-drive or peripheral bus to interconnect the PC

mother board and a hard drive. The IDE bus is a Parallel bus. With the

introduction of the Serial ATA [SATA] specification Parallel

ATA [IDE] is now being called PATA. |

There are a number of versions of the ATA bus, with each of the different versions listed below. The Serial ATA: which replaced the ATA bus is listed on its own page. Details for each bus version are listed below. A graphic which provides a comparison of all the different IDE interfaces listed here is provided on the HardDrive Interface Speed page.

ATA-1 (IDE), [Obsolete] 8.3MBytes/sec, 8 or 16 bit data

width, 40 pin data ribbon cable/connector. With a maximum of 2 devices on

the bus. Using PIO Modes 0, 1 or 2. Performed no bus error correction.

The ATA-1 specification was released in 1994, and was withdrawn in

1999.

ATA-2 (EIDE, or Fast ATA), [Obsolete] 16.6MBytes/sec, 8 or

16 bit data width, 40 pin data ribbon cable/connector. With a maximum of

4 devices on the bus. Using PIO Modes 0, 1, 2, 3, or 4. The ATA-2

specification was released in 1995 and was withdrawn in 2001.

ATA-3, 16MBytes/sec, 16 bit data width, 40 pin data ribbon

cable/connector. Using PIO Modes 0, 1, 2, 3, or 4 and Multiword DMA modes

1 and 2. Runs with 120nS Strobes (rising edge to rising edge). Includes

CRC.

ATAPI (ATA Packet Interface) is the CD-ROM side of the interface.

It uses the same connector as ATA, and adds 1 for analog and 1 for

digital audio. The ATA-3 specification was released in 1997 and was

withdrawn in 2002.

ATA-4 Ultra-ATA/33, 33MBytes/sec, 16 bit data width, 40 pin data

ribbon cable/connector. Using PIO Modes 0, 1, 2, 3, or 4 and Multiword

DMA modes 1 and 2 and Ultra DMA modes 0, 1, and 2. Runs with 120nS

Strobes (rising edge to rising edge), but used both edges of the Strobe

producing an effective 60nS Strobe rate. 33MBps Transfer speed =

[(1/120nS) x 2 bytes x 2]. Where 120nS cycle time is 4 clock periods at

30nS each. Added CRC checking. The ATA-4 standard was released in

1998.

ATA-5 Ultra-ATA/66, 66MBytes/sec, 16 bit data width 40 pin data

connector/80 pin cable, with the additional 40 new pins being Ground. The

new cable allows ATA/66 to run at a faster rate then ATA/33. Using PIO

Modes 0, 1, 2, 3, or 4 and Multiword DMA modes 1 and 2 and Ultra DMA

modes 0, 1, 2, 3 and 4. Runs with 60nS Strobes (rising edge to rising

edge), but uses both edges of the Strobe producing an effective 30nS

Strobe rate. 66MBps Transfer speed = [(1/60nS) x 2 bytes x 2]. Where 60nS

cycle time is 2 clock periods at 30nS each. The ATA-5 standard was

released in 2000.

ATA-6 Ultra-ATA/100, 100MBytes/sec,16 bit data width 40 pin data

connector/80 pin cable, with the additional 40 new pins being Ground.

Using PIO Modes 0, 1, 2, 3, or 4 and Multiword DMA modes 1 and 2 and

Ultra DMA modes 0, 1, 2, 3, 4 and 5. 100MBps Transfer speed = [(1/40nS) x

2 bytes x 2]. Where 40nS cycle time is 2 clock periods at 20nS each. The

ATA-6 standard was released in 2002.

ATA-7 Ultra-ATA/133, 133MBytes/sec,16 bit data width 40 pin data

connector/80 pin cable, with the additional 40 new pins being Ground.

Using PIO Modes 0, 1, 2, 3, or 4 and Multiword DMA modes 0, 1 and 2 and

Ultra DMA modes 0, 1, 2, 3, 4, 5 and 6. 133MBps Transfer speed =

[(1/30nS) x 2 bytes x 2]. Where 30nS cycle time is 2 clock periods at

15nS each. The ATA-7 standard was released in 2005. With the introduction

of Serial ATA, this is the last expected update of the IDE [PATA] bus.

SATA is faster, and requires a smaller

cable, which means better air flow in the Case.

Serial ATA: (Ver 1.0) High Speed

Serialized AT Attachment

Serial version of the IDE [ATA] spec. Uses a 4 conductor cable with two

differential pairs [Tx/Rx], plus an additional three grounds pins and a

separate power pin. Data runs at 150MBps [1.5GHz] using 8B/10B

encoding and 250mV signal swings. Serial ATA is not compatible with the

IDE [Parallel ATA] because the connectors are different, the voltage

levels are different, and data format is different [SATA sends a bit at a

time while PATA sends 16 bits at once]. SATA will not interface with

the IDE bus. No cable can be made to connect SATA with IDE. However a

converter may be purchased which translates SATA to PATA. One module

appears as a 2" x 2" board, for $50 and converts IDE controllers

66/100/133/150 MB/s to Serial ATA 150.

ATA-# interface for disk drives; defines the Physical layer, Electrical

layer and Signaling protocol. The speed of data transfer depends on the

Transfer mode used. There are 3 main Transfer modes: PIO, Multiword DMA,

and Ultra DMA. All transfer rates listed above are best case

[Mulit-word/DMA transfers].

PIO Modes: 0 [3.3MB/s], 1 [5.2MB/s], 2

[8.3MB/s], 3 [11.1MB/s], 4 [16.7MB/s]

Multiword DMA Modes: 0 [4.2MB/s], 1 [13.3MB/s],

2 [16.7MB/s]

Ultra DMA Modes: 0 [16.7MB/s], 1 [25.0MB/s],

2 [33.3MB/s], 3 [44.4MB/s], 4 [66.7MB/s], 5

[100.0MB/s]

The hard drive, computer, and software determine the mode used:

Programmed Input/Output (PIO), Direct Memory Access (DMA). Addressing on

the bus is defined by; CHS (Cylinder, Head, Sector)

Power (+5 / +12volts) is supplied over a four pin connector (unless the

50-pin connector is used). There are a number of power (down) modes

defined: Active, Idle, Standby, and Sleep.

Active: normal drive operation.

Idle: the electronics power down but still receives

commands.

Standby: the drive spins down and the electronics power

down.

Sleep: every thing is powered down, the electronics will not

respond except for a power reset.

The early specifications defined the data cable as a normal 40 pin ribbon

cable with a 40 pin IDC connector. The latest standard(s) define the same

40 pin connector, but have increased the ribbon to 80 pins - the

additional 40 pins being dedicated to ground pins. Data transfers are

made at either 8 or 16 bits.

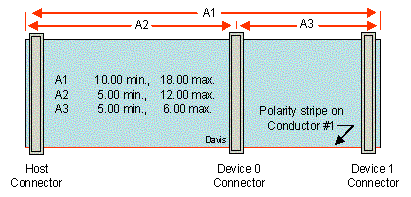

The normal PC cables have three connectors, one for the mother board (at

one end) and two for device attachment. One at the opposite end, the

other about 6 inches away.

Data is carried at standard TTL levels over the Parallel ATA [PATA]

interface, or IDE interface.

A chart comparing TTL and CMOS threshold levels is provided on the

Logic Threshold Voltage Levels

page.

The bus is source [series] terminated with a 33 ohm resistor. This

page lists Glue Logic TTL devices.

----------------------

Cirrus Logic {Disk Controller ICs}

HighPoint Technologies, Inc. {ATA 100/ 133 non-RAID / RAID Disk Controller, RAID 0, 1, 5, 10, JBOD}

Hitachi {ATA-5 compliant memory controller, Mode 4 (66.6 Mbytes/sec)}

Silicon Image Inc {Ultra ATA/100 PCI to ATA Host Controllers}

Silicon Storage Technology, Inc. 'SST' {ATA Flash Disk Controller}

Winbond Electronics Corp. {Power PC I/O Controller-Port Controller-IDE Interface-CDROM Decoder}

Zilog {PCMCIA / Storage Controller ICs}

Another listing of PC Chip Set Manufacturers

Ultra ATA doubles the data transfer rate (over Fast ATA) by using the both edges of the strobe

T13 {Technical Committee T13; AT Attachment}

{Hit the link above to down load the current draft specifications

from each working group. Keep in mind that only work on version 7 and 8

are active.

Also that these specification come in multiple volumes, and only the

Physical portion is listed below. The rev level indicated may not be the

latest.}

ATA-1; AT Attachment Interface (ATA-1); American National Standard

X3.221-1994

ATA-2; AT Attachment Interface with Extensions (ATA-2) (ANSI

X3T10/948D Rev. 3)

ATA-3; AT Attachment Interface (ATA-3) (ANSI X3T10/2008D Rev.

7b)

ATAPI; AT Attachment with Packet Interface (ATAPI) (X3T10/1120D

Rev. 2)

ATA/ATAPI-4; AT Attachment with Packet Interface Extension

(ATA/ATAPI-4) (T13/1153D Rev. 18)

ATA/ATAPI-5; AT Attachment with Packet Interface Extension

(ATA/ATAPI-5) (T13/1321D Rev. 3)

ATA/ATAPI-6; AT Attachment with Packet Interface Extension

(ATA/ATAPI-6) (T13/1410D Rev. 3b)

ATA/ATAPI-7; AT Attachment with Packet Interface Extension

(ATA/ATAPI-7) (T13/1532D Vol 1 Rev. 2)

ATA/ATAPI-7; AT Attachment with Packet Interface Extension

(ATA/ATAPI-7) (T13/1532D Vol 2 Rev. 2)

ATA/ATAPI-7; AT Attachment with Packet Interface Extension

(ATA/ATAPI-7) (T13/1532D Vol 3 Rev. 2)

AT Attachment - 8 ATA/ATAPI; Parallel Transport (ATA8/APT)

ATA/ATAPI-8; AT Attachment Serial Transport / Parallel Transport &

Command Set (ATA/ATAPI-8)

Currently the latest released version is revision 7. ATA/ATAPI-8 has not

yet been released, and as noted seen with two different titles.

I don't expect any additional IDE Specifications to be released, after the ATA-8 IDE Specification

Serial ATA: (Ver 1.0) High Speed

Serialized AT Attachment

Serial version of the IDE [ATA] spec. Uses a 4 conductor cable with two

differential pairs [Tx/Rx].

Data runs at 150MBps [1.5GHz] using 8B/10B

encoding and 250mV signal swings.

Power (4 pin connector, 0.2 centers), uses an 18 AWG cable;

A separate connector does not exist on all types of interfaces, CardBus for example.

1: +12volt

2: +12v Ground [GND]

3: +5v Ground [GND]

4: +5volt

Data (70 to 90 ohms cable impedance, 30 AWG wire size, IDC termination)

..... (ATA-1 to ATA-4) 40 pin ribbon / IDC connector / flat cable

(stranded 28AWG) 18 inches in length [Maximum cable length]

..... (ATA-5 / ATA-6) 80 pin ribbon/IDC cable, 40 pin connector, which

will mate with ATA-2/ATA-1, 18 inches in length (12 inches host to device

0, 6in device 0 to 1).

The drive connector is a 40 pin header; with 2 rows of 20, at 0.1 inch

spacing. The 40 pin cable requires an additional power cable. The

connector is keyed, with pin 20 removed, the mating IDE connector should

have the socket of pin 20 blocked, it may be polarized [IDC Definition]. The data and

power may be combined into one hybrid connector. Also, there may be a 44

pin header which is used. Placed before pin 1, will be a key, followed by

two sets of pins which may be used by the board. The additional pins are

not transmitted over the 40 pin cable. An additional 68-pin connector is

defined by the standard. The 68-pin connector is the same used by

PCMCIA, and allows the device to be

compliant with PC Card ATA mode.

Circuit Assembly Corp. {IDE Connectors Disk Drive/Headers}

Foxconn Electronics {IDE Connector}

For cables to function properly in ATA applications, the first connector should be the "Blue" connector. If using a two connector assembly, the second connector should be the "Black" connector. If a three connector cable is required all three "Blue, Gray & Black" connectors should be used in the proper order with "Blue" and "Black" on the ends with "Gray" in the middle. The end may be terminated so that they both face in one direction or with one facing up and the other facing down.

| Pin # | Signal Function | Pin # | Signal Function |

| 1 | Reset | 2 | Ground |

| 3 | Data 7 | 4 | Data 8 |

| 5 | Data 6 | 6 | Data 9 |

| 7 | Data 5 | 8 | Data 10 |

| 9 | Data 4 | 10 | Data 11 |

| 11 | Data 3 | 12 | Data 12 |

| 13 | Data 2 | 14 | Data 13 |

| 15 | Data 1 | 16 | Data 14 |

| 17 | Data 0 | 18 | Data 15 |

| 19 | Ground | 20 | Key [Void] |

| 21 | DMARQ | 22 | Ground |

| 23 | DIOW- | 24 | Ground |

| 25 | DIOR- | 26 | Ground |

| 27 | IORDY | 28 | CSEL |

| 29 | DMARK- | 30 | Ground |

| 31 | INTRQ | 32 | IOCS16- |

| 33 | DA1 | 34 | PDIAG- |

| 35 | DA0 | 36 | DA2 |

| 37 | CS1FX- | 38 | CS3FX- |

| 39 | DASP- | 40 | Ground |

The 40 pin ATA connector pinout and cable pinout is shown above. The 80 pin cable pinout is about the same as above, except that all the signal names listed above are now odd pins in the cable; how ever it's still a 40 pin connector so the table is true for the connector but not the 80 pin cable. The 80-pin cable has all the even cable wires connected to ground. So each pin listed above after pin 1 moves down one or more pin numbers. Pin 2 [Ground] moves to pin 3, Pin 3 has to move to pin 5, Pin 4 has to move to pin 7, pin 5 has to move to pin 9, and so on; using only odd number pins - as all even conductors in the cable are used for ground. At the end of the list pin 40 [ground] is pin 79, while pin 80 is also ground [even pin]. The only exception is pin 34 [PDIAG] which is connected to ground in the cable. Which makes both pin 67 and 68 ground pins in the cable. True for the 80-pin cable, remember the connector remains unchanged, only the cable pin-out changes.

| Pin # | Signal Function | 18 AWG Wire |

| 1 | +12V DC | Yellow |

| 2 | +12V Return | Black |

| 3 | +5V Return | Black |

| 4 | +5V DC | Red |

Recommended wire size is 18AWG. for the power supply interface. The wire color codes were derived from the ATX Motherboard specification.

This is a general listing of Personal Computer IDE Hard drive

manufacturers.

There is another listing for other bus interface types

which may be found on the Computer Hard Drive Manufactures

page.

The different types of disk drive bus interface types are listed

below. Keep in mind that the Parallel ATA [PATA] Bus is being replaced by

the Serial ATA: [SATA] bus.

Internal Interface types; ATA, Ultra ATA, SATA [Desk-top],

SCSI, Ultra

SCSI, Serial SCSI, SATA [Enterprise]

External Interface types; SATA

[Desktop], SCSI, Serial SCSI [Enterprise], Fibre

Channel [Enterprise]

Adtron Corporation {Solid State IDE 2.5" UDMA-100, IDE 3.5" UDMA-66, RAID}

Fujitsu {Modile 2.5 inch IDE}

Hitachi {2.5 inch ATA-5 hard disk drive}

HP {160GB Ultra ATA/100}

Samsung {Ultra ATA - 100}

Seagate Disc Storage {Ultra ATA/100}

Toshiba Hard Drives {1.8"; 80GB/120GB/240GB, 100MBps Ultra DMA, Parallel ATA (PATA), 4200rpm}

Western Digital Corp. {SATA 150MBps, SATA 300MBps, EIDE Drive, Enterprise, Desktop, Mobile, External Hard Disk Drives}

| |||||||

| Home | |||||||

|

|

|

|

|

|

|

|

| Distributors | Components | Equipment | Software | Standards | Buses | Design | Reference |